1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. Panel DL 2203C

2. Panel DL 2203D

3. Panel DL 2203S

4. Jumper

5. J-K Flip-Flop

6. Clock

7. Gerbang AND

3. Rangkaian [Kembali]

4. Prinsip Kerja [Kembali]

Pada percobaan ini, dibuat rangkain pada Module D'Lorenzo seperti yang ada pada gambar di modul.

Percobaan ini merupakan rangkaian shift register dengan menggunakan 4 buah JK flip flop yang berarti memiliki 4 bit. Setelah di rangkai, jalankan rangkaian dengan memvariasikan B0-B6 pada tiap kondisi sesuai dengan ketentuan yang ada pada jurnal. Kemudian, analisa input dan output yang terjadi pada rangkaian dan tentukan jenis shift register pada tiap kondisi (SISO, SIPO, PISO, atau PIPO)

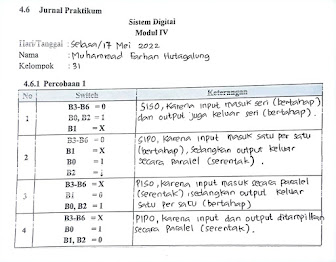

Percobaan 1

1. Analisa output yang dihasilkan tiap-tiap kondisi

Jawab:

• Kondisi Pertama:

B3-B6=0

B0, B2=1

B1 = X (don't care /sebagai masukan)

Pada Kondisi ini menunjukkan jenis shift register SISO (Serial in Serial out), dikarenakan input masuk Secara seri (bertahap 7 dan output juga Keluar secara seri (bertahap).

• Kondisi Kedua:

B3-B6=0

B1 =X

B0= 1

B2: ↓ (fall time, dari 1 ke 0)

Pada kondisi ini menunjukkan Jenis shift register SIPO (Serial in Paralel out), dikarenakan input masuk satu Per Satu (bertahap), sedangkan output Keluar secara paralel (serentak).

• Kondisi Ketiga:

B3-B6 =X

B1 =0

B0, B2 =1

Pada Kondisi ini menunjukkan jenis shift register Piso (paralel in serial out), dikarenakan input masuk Secara paralel (serentak), sedangkan output keluar Satu per satu (bertahap).

•Kondisi Keempat :

B3-B6=X

B0=1

B1, B2 =0

Pada Kondisi ini menunjukkan jenis shift register PIPO (Paralel in paralel out), dikarenakan input masuk secara Paralel (serentak), dan outpul juga keluar secara Paralel (serentak).

2. Jika gerbang AND Pada rangkaian dihapus, sumber clock langsung dihubungkan ke flip flop, bandingkan output yang didapatkan.

Jawab:

Pada saat kondisi SISO, apabila gerbang AND dihapus dan clock dihubungkan ke Flip flop, output rangkaian tidak terpengaruhi.

Gerbang AND ditambahkan agar pada saat switch yang disandingkan pada gerbang AND berlogika 0 maka output. clock tidak aktif sehingga output dapat di keluarkan secara paralel.Maka jika gerbang AND dihapus, maka output rangkaian shift register tidak dapat berfungsi secara paralel.

Tidak ada komentar:

Posting Komentar